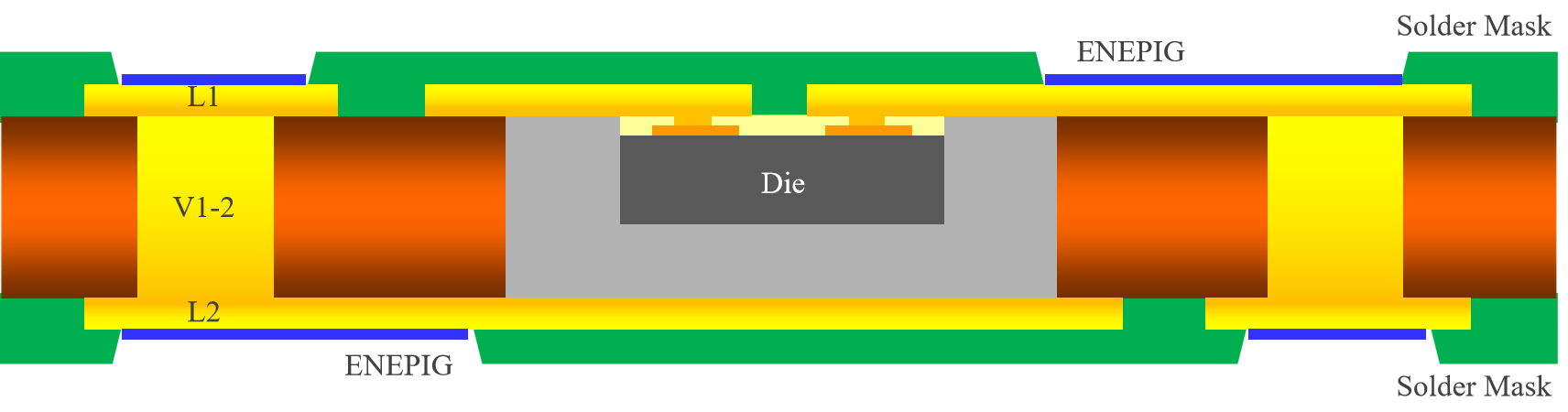

A new type of packaging method in which the chip or passive components are embedded between the metal layers inside the substrate, and the I/O of the chip or device are fan-out to the external pin through the micro-vias and metal layers. This chip embedded substrate allows surface area on top to place additional chips and passives devices on the top surface to gain higher integrated level of functionality in 3D stack-up. By using this innovated and customized process, all the components can be integrated in one packaged to form a new system-level package or module.

The chip embedded substrate can support 1~7 fanout layers, and realize a 3D integrated structure

The chip embedded substrate can support 1~7 fanout layers, and realize a 3D integrated structure Manufactured using ACCESS independent intellectual property (IP), and compatible with traditional MSAP process, that allows extensive chip and passive component integration

Manufactured using ACCESS independent intellectual property (IP), and compatible with traditional MSAP process, that allows extensive chip and passive component integration Seamless connection between chip and carrier board using wafer-like process with thin film Sputtering Ti/Cu (Sputter Ti/Cu)

Seamless connection between chip and carrier board using wafer-like process with thin film Sputtering Ti/Cu (Sputter Ti/Cu) The connection between the chip and the substrate is formed through Sputtering a seed layer of thin metal film (Ti/Cu) in the wafer-like process, which significantly improves the electrical performance and heat dissipation effect, as well as the long-term reliability

The connection between the chip and the substrate is formed through Sputtering a seed layer of thin metal film (Ti/Cu) in the wafer-like process, which significantly improves the electrical performance and heat dissipation effect, as well as the long-term reliability Flexible advanced design rules can achieve thinner and smaller formfactor devices than the traditional semiconductor package

Flexible advanced design rules can achieve thinner and smaller formfactor devices than the traditional semiconductor package The process is a Panel Level Fanout that can achieve lower cost structures than current packages processed using Wire bond, or Flip Chip technologies

The process is a Panel Level Fanout that can achieve lower cost structures than current packages processed using Wire bond, or Flip Chip technologies